The Critical Bottleneck in CPO Mass Production? It's Testing

A complete breakdown of CPO testing stages, and the competitive landscape among Advantest, Teradyne, Keysight, and other equipment vendors.

TrendForce 2026 New York Roadshow arrives May 12. We’re decoding the AI-driven market inflections in memory and foundry — and what they mean for the 2026–2028 supercycle: REGISTER HERE.

As AI data center clusters continue to scale, the demand for data movement has surged, pushing traditional copper interconnects to their physical limits. CPO is now widely regarded as one of the key interconnect solutions for next-generation AI infrastructure. With TSMC’s COUPE platform projected to enter volume production in 2026, CPO is making its transition from the lab toward commercialization.

However, the CPO inspection and testing phase remains a significant hurdle. Currently, the industry lacks unified standards, and processes remain largely manual, making testing one of the major bottlenecks holding back CPO chip mass production.

This article examines the technical challenges of CPO testing, provides a detailed breakdown of the four critical testing stages, and maps out the existing solutions and technical advantages of equipment vendors.

Related report: AI Interconnect Outlook: NVIDIA Leads the Transition to CPO and Silicon Photonics Architectures

What Makes CPO Testing So Challenging

Co-Packaged Optics (CPO) integrates optical components into a Photonic Integrated Circuit (PIC), which is then co-packaged with an Electrical Integrated Circuit (EIC) in a single chip. By replacing electrical traces with optical paths, CPO reduces power consumption and latency. The bonded PIC-EIC assembly is called an Optical Engine (OE).

TSMC’s COUPE (Compact Universal Photonic Engine) is one such implementation, using SoIC Face-to-Face (F2F) stacking to hybrid-bond the EIC directly onto the PIC, incorporating shallow dielectric vias (TDV), embedded microlenses, and metal reflectors.

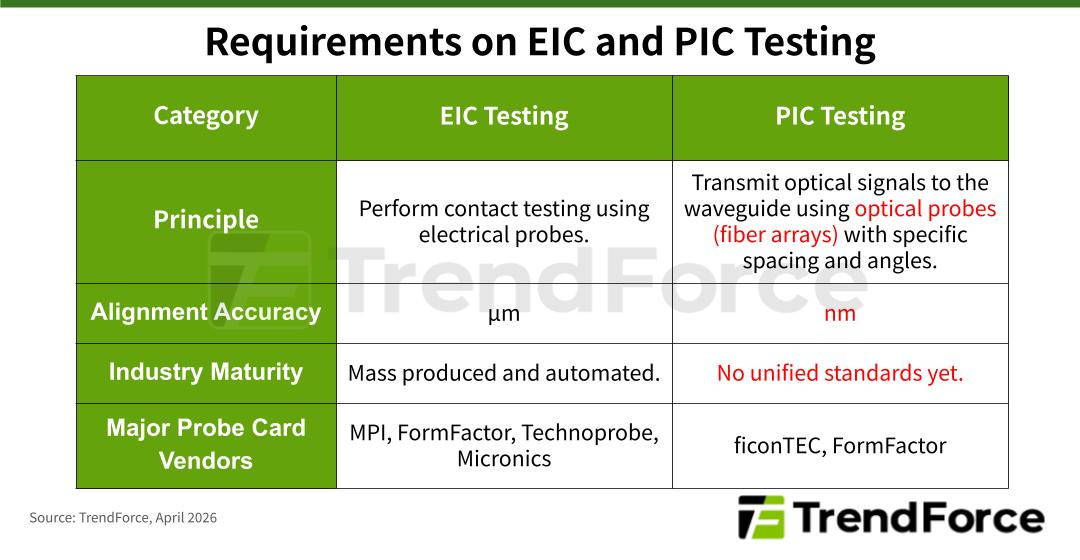

Unlike traditional EIC testing, which is purely electrical, a PIC contains a large number of optical components such as couplers, modulators, photodetectors (PD), optical filters, and optical waveguides. Testing an OE requires expertise across electrical, optical, and optoelectronic interactions, significantly increasing test complexity.

PIC testing must measure parameters such as insertion loss (IL), polarization-dependent loss (PDL), responsivity, waveguide propagation loss, and optical crosstalk. However, there is currently no unified test standard for these.

In addition, precise alignment of optical probes is a major challenge. The technique of guiding external light from an optical fiber into the OE’s optical waveguide is called optical coupling. However, a single-mode fiber core has a cross‑sectional area of about 78.5µm², while that of an optical waveguide is only about 0.099µm², a difference of nearly 800 times. Without nanometer-level alignment precision, coupling loss will be enormous.

Therefore, the fiber array of the optical probe must maintain a precise gap from the wafer or die surface while finely adjusting its angle relative to the coupler to maximize optical power transfer, and then perform measurements sequentially across different wavelength ranges. Such delicate operations currently rely on manual handling, with 100% inspection of a single PIC taking on average more than 100 seconds, making this one of the key bottlenecks for mass production of CPO chips.

The Four Testing Stages, and Why OWAT Matters Most

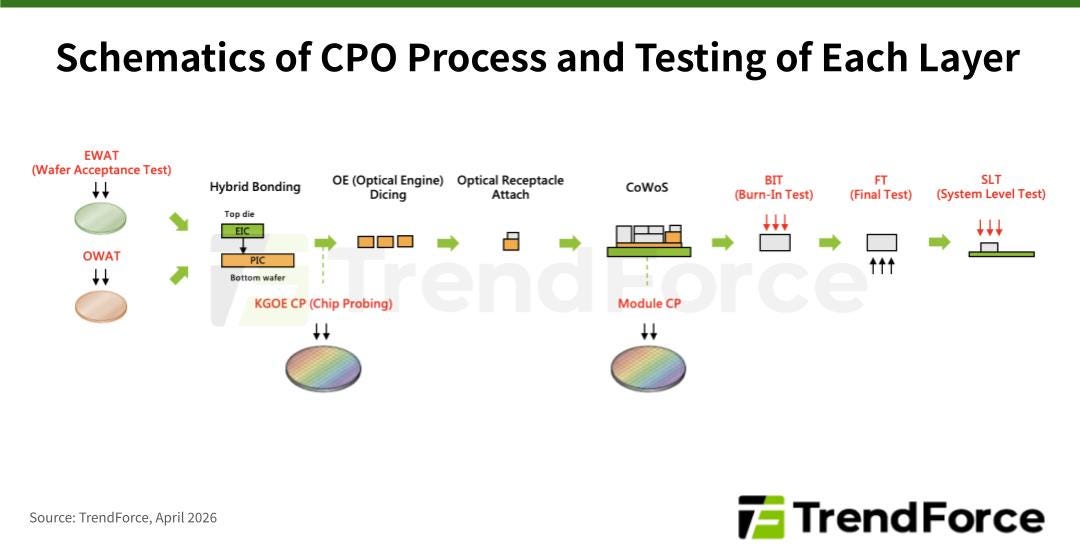

The testing stages required for a single CPO chip are:

(1) PIC wafer‑level test: DC electrical and optical tests, such as basic optical measurements of power, loss, dark current, etc.

(2) EIC‑PIC wafer‑level test: modulation‑function tests (electro‑optic, opto‑electric, and opto‑optic), high‑speed tests, and S‑parameter measurements.

(3) OE‑level test: full‑flow calibration, DC tests, high‑speed tests, optical loop‑back tests, and S‑parameter measurements. This is the key stage for confirming “Known Good Optical Engines” (KGOE).

(4) Advanced‑package module‑level test: full system functional verification and optical loop‑back tests.

Among these, PIC wafer-level test, also known as OWAT, is the most critical stage. While PICs are typically fabricated on mature process nodes, EICs generally use advanced nodes. If defective PICs can be identified already at the wafer stage, before bonding with expensive EICs, then scrapping of EICs and subsequent process losses can be greatly reduced.

Competitive Structure of Supply Chain

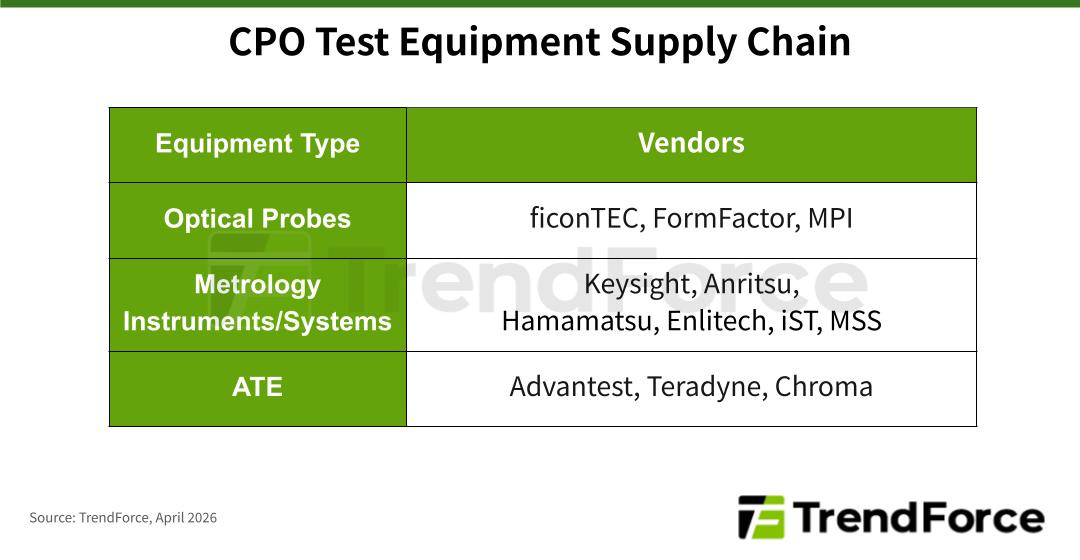

Traditional EIC automated test equipment (ATE) market is dominated by Japan’s Advantest and the US’s Teradyne. Since developing CPO test equipment requires expertise in both EIC and PIC testing, both vendors have pursued partnerships with PIC probe specialists: Advantest with FormFactor, and Teradyne through its 2025 acquisition of Quantifi Photonics and collaboration with ficonTEC.

Advantest & FormFactor

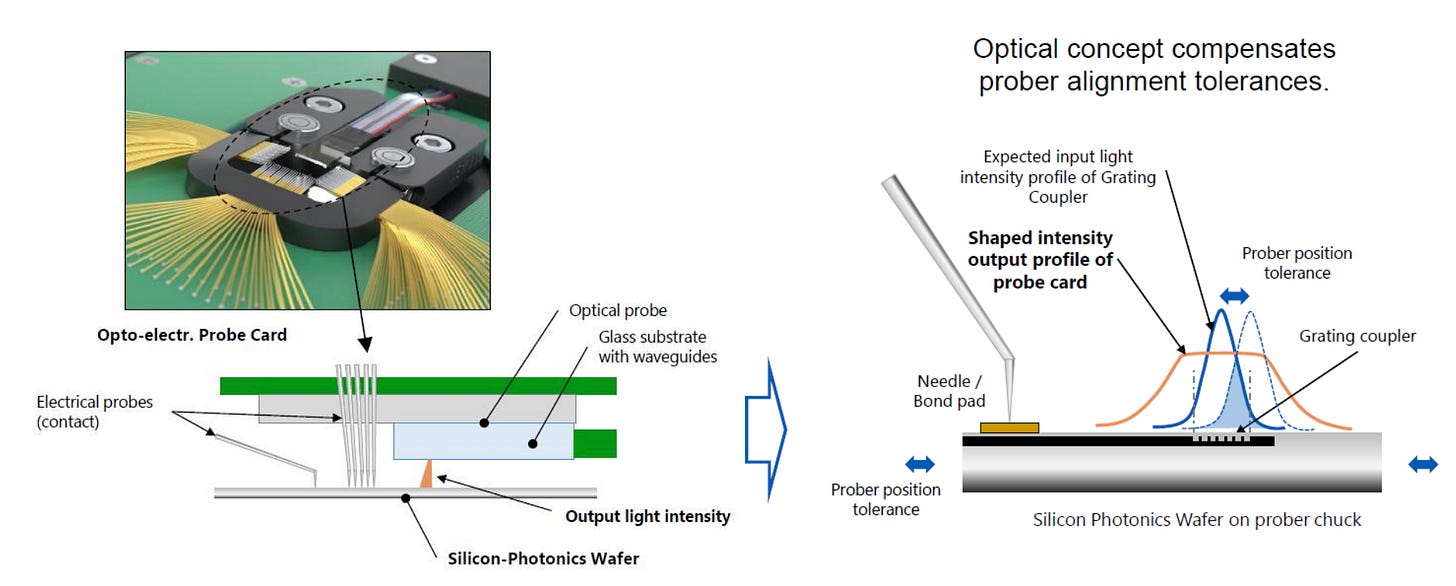

In June 2024, Advantest, Jenoptik, and Ayar Labs jointly launched the UFO Probe Card, integrating both electrical and optical probes on a single card for simultaneous electro-optical testing. Its key innovation is alignment tolerance compensation technology: the optical probe’s output beam is specifically shaped, allowing the optical signal to enter the PIC coupler even with slight prober positioning errors, greatly reducing alignment time.

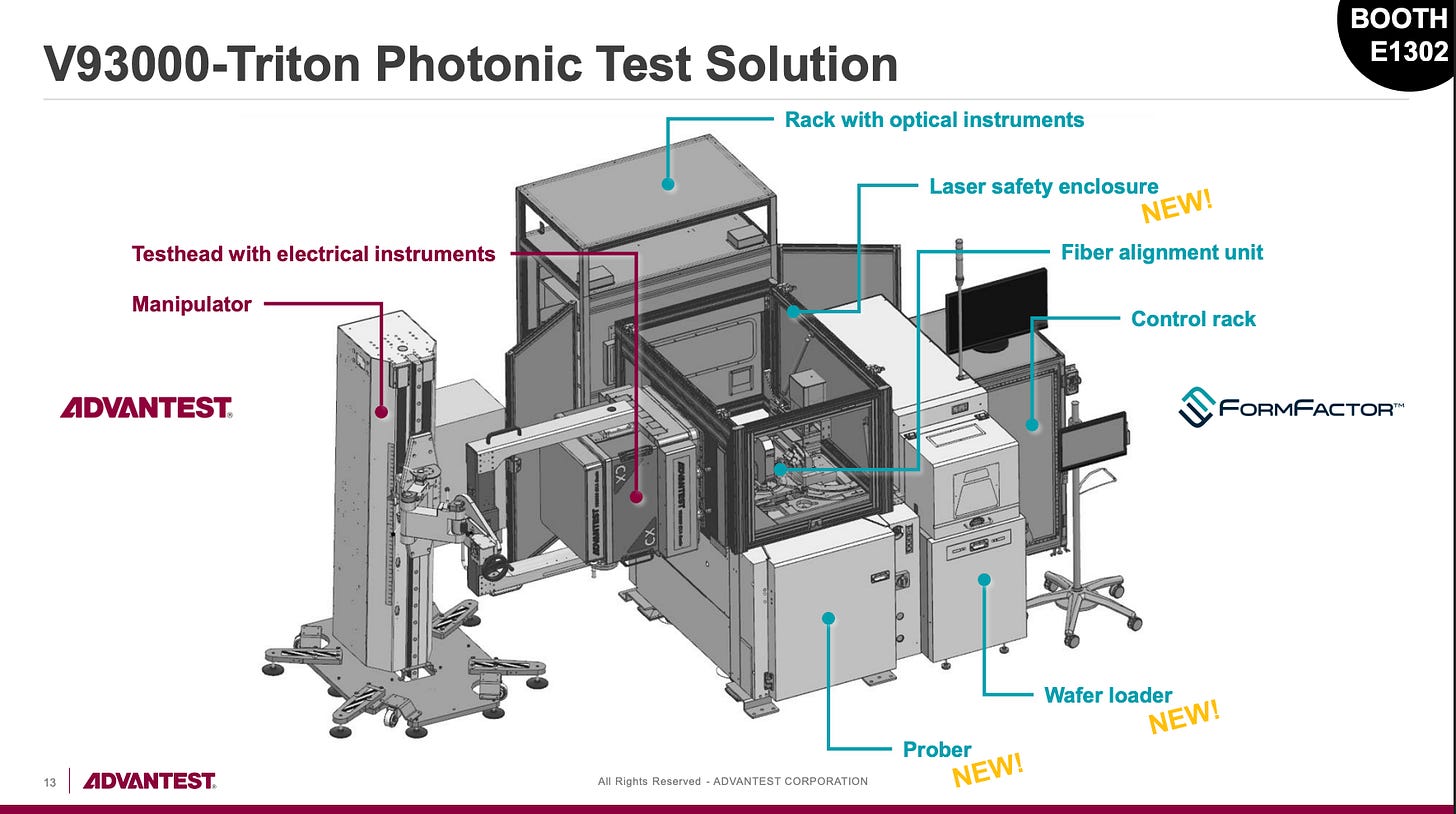

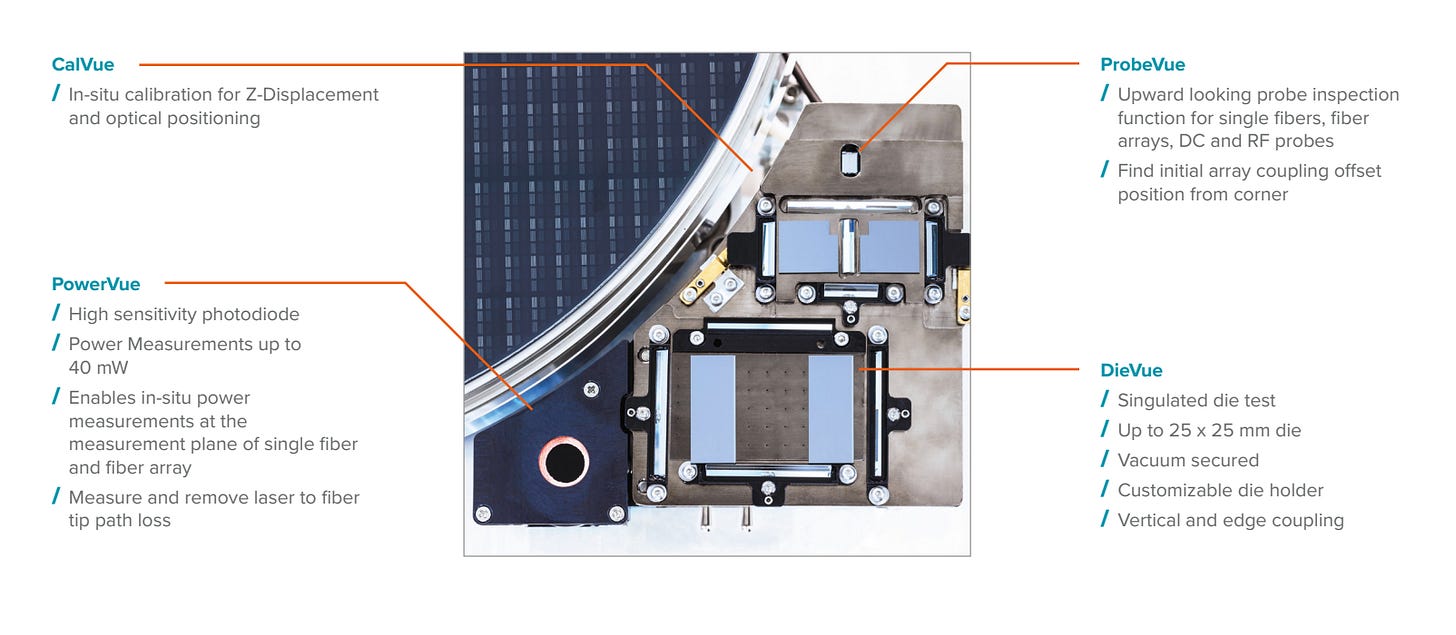

In April 2025, Advantest and FormFactor launched the V93000-Triton photonic test system, featuring 9-axis photonic alignment and FormFactor’s OptoVue Pro optical alignment system. Its CalVue technology enables in-situ calibration of Z-axis displacement and optical positioning by observing the fiber array via uniquely designed retro-mirror technology and applying automated machine-vision algorithms in real time, reducing fiber alignment time.

Teradyne & ficonTEC

In March 2025, Teradyne and Germany’s ficonTEC (now a subsidiary of China’s Robo Technik) announced the industry’s first high-volume 300 mm double‑sided wafer probe test system for silicon photonics. ficonTEC provides the WLT‑D2 double‑sided wafer test platform, which features 50 nm‑range precision alignment, while Teradyne supplies the UltraFLEXplus ATE and IG‑XL system software.

A key feature of ficonTEC’s WLT‑D2 is its dual‑sided test capability, enabling simultaneous electrical testing on the top surface and optical testing on the bottom surface of the wafer, thereby improving test efficiency. The subsequent DLT‑D1 is a dual‑sided die‑level test system that can connect up to three parallel test heads simultaneously, increasing throughput and reducing test cost. With the addition of the DLT‑D1, ficonTEC now offers a complete CPO test product portfolio from wafer‑level to die‑level.

Chroma

Chroma is the global leader in SLT equipment. Its photodiode burn‑in and reliability test systems, the Model 58604/58604‑C/58606 series, are designed for reliability testing of PIC components such as 3D sensing devices, LDs, PDs, and modulators. The Model 58606 provides 256 SMU channels per module layer, and can be configured with up to 7 layers, for a total of 1,792 channels. Leveraging its optical test expertise at the SLT stage, Chroma has also announced that it is investing in the development of CPO test equipment.

Keysight

Keysight, the global leader in measurement instruments, is well known for its high‑speed test equipment and also provides a complete PIC wafer‑test solution. Keysight’s PIC wafer‑test solution is integrated with FormFactor, and is compatible with FormFactor’s Velox prober control software.

Keysight’s N778x series polarization synthesizers can rapidly switch the incident light among different States of Polarization (SOP), and, together with the N7700100C Polarization Lambda Scan (LS) software, uses matrix methods to derive IL, PDL, TE/TM IL, and other parameters. Therefore, this solution does not need polarization‑maintaining fiber (PMF), nor does it require prior manual polarization correction at multiple wavelength points, greatly increasing test efficiency. In addition, its SOP stabilization technology can lock the input light’s polarization state at a specific point, ensuring stable optical coupling throughout the entire wavelength sweep.

Enlitech

In September 2025, Enlitech partnered with iST to launch Night Jar, a SiPh chip testing platform. Designed as an add-on hyperspectral imaging analysis system, it can be directly mounted onto probe stations of any brand across various testing stages (WAT, CP, FT, etc.). This platform addresses long-standing industry pain points: previously, light leakage locations in optical waveguides could only be roughly estimated using reflected light, yielding only total or average optical loss values.

The Night Jar platform is distinguished by its ability to precisely pinpoint light leakage and measure quantitative IL values for specific waveguide segments or optical components. By visually mapping these metrics and supporting wafer-level optical loss mapping, the platform enables R&D personnel to identify defects more accurately and rapidly, ultimately improving production yields.

Market Opportunities

As chip designs grow increasingly complex, the difficulty of SoC testing has risen significantly. The number of test stations and the overall testing time required for a single chip continue to increase, driving up the share of test equipment within total semiconductor equipment capital expenditures. As CPO chips are integrated into product portfolios, the semiconductor sector’s capital expenditures on test equipment are expected to climb even further.

The CPO test equipment market is taking shape, and knowing the competitive landscape matters. For the comprehensive supply chain and market analysis, access the full report:

CPO Testing Revolution: Market Opportunities in Co-Packaged Optics Validation